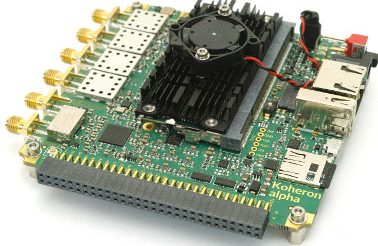

250 MSPS acquisition board(型番:ALPHA250)

ALPHA250は、Zynq 7020 SoCを中心に構築されたプログラマブル・ボードである。250 Mspsの14ビットADCと16ビットDACを備えた100 MHz RFフロントエンドを搭載している。RFチャンネルは、デュアルPLL、超低ジッター・クロック・ジェネレーターによってクロック供給される。このボードには、4チャネル24ビットADCと4チャネル16ビットDACが搭載されています。このボードには、包括的なオープンソースのFPGA / Linuxリファレンス・デザインが付属しています。

付属品

12 V 1.5 A電源

OSをプリインストールしたマイクロSDカード

仕様(一部を抜粋)

| ALPHA250 | ALPHA250-4 | |

|---|---|---|

| Programmable logic, processor and memory | ||

| System On Chip | Zynq 7020 XC7Z020-2CLG400I | Zynq 7020 XC7Z020-2CLG400I |

| Memory | 512 MB of DDR3L SDRAM | 512 MB of DDR3L SDRAM |

| Processor | ARM dual-core CPU (Cortex-A9) | ARM dual-core CPU (Cortex-A9) |

| RF ADC | ||

| Number of channels | 2 | 4 |

| Resolution | 14-bit | 14-bit |

| Sampling rate | 250 Msps | 250 Msps |

| Coupling | DC | DC |

| Input impedance | 50 Ω | 50 Ω |

| Input range | 1 Vpp | 1 Vpp |

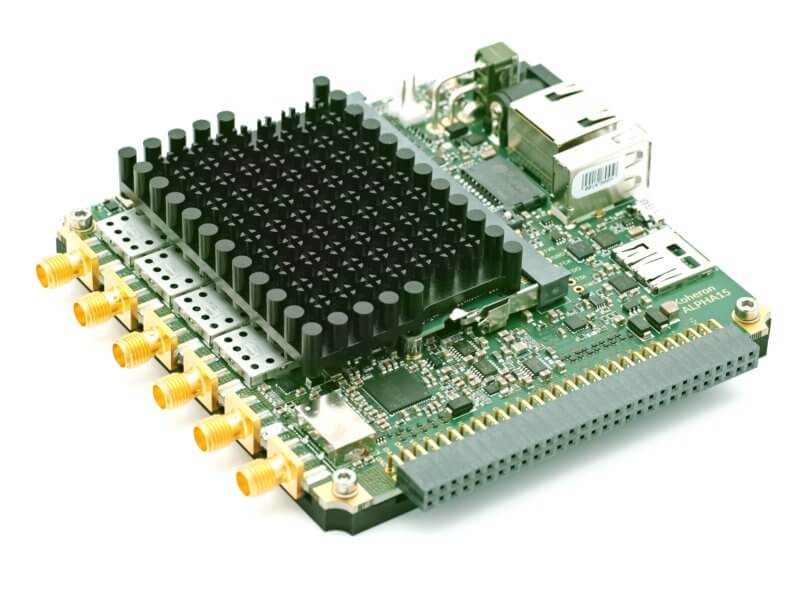

18-bit 15 Msps acquisition board(型番:ALPHA15)

ALPHA15は、Zynq 7020 SoCを中心に構築されたプログラマブル・ボードです。高ダイナミック・レンジ、低ノイズのフロントエンドを備えた2つの18ビット15 Msps ADCを搭載している。高入力インピーダンス(最大1 MΩ)は駆動が容易で、センサーとの直接インターフェースが可能です。入力レンジは、2 Vpp(± 1 V)または8 Vpp(± 4 V)の2種類から選択可能です。ALPHA15は、フリッカーノイズのコーナー周波数が非常に低い(50 Hz以下)ため、高いオーバーサンプリングアプリケーションに最適です。ALPHA15はまた、デュアルチャネル16ビット250 Msps低レイテンシDACと4チャネル16ビット精密DACを備えています。高速データ・コンバータは、デュアルPLL、超低ジッタ・クロック・ジェネレータによってクロック供給されます。このボードには、包括的なオープンソースのFPGA/Linuxリファレンス・デザインが付属しています。

付属品

12 V 1.5 A電源

OSをプリインストールしたマイクロSDカード

仕様(一部を抜粋)

| ALPHA15-1M | |

|---|---|

| Programmable logic, processor and memory | |

| System On Chip | Zynq 7020 XC7Z020-2CLG400I |

| Memory | 512 MB of DDR3L SDRAM |

| Processor | ARM dual-core CPU (Cortex-A9) |

| 18-bit ADC | |

| Number of channels | 2 |

| Resolution | 18-bit |

| Sampling rate | 15 Msps |

| Coupling | DC |

| Input impedance | 1 MΩ |

| Flicker noise corner frequency | 50 Hz |

| Input range | 2 Vpp or 8 Vpp |

| Crosstalk | < 120 dB |

| Input-referred voltage noise 10 kHz, 50 Ω input, 2 V range |

7 nV/√Hz |

| Input-referred voltage noise 10 kHz, 50 Ω input, 8 V range |

18 nV/√Hz |

| Total harmonic distortion 2 kHz, -3 dBFS, 8 V range |

-105 dB |

| Effective number of bits 2 kHz, -3 dBFS, 8 V range |

15 bits |